行业新闻

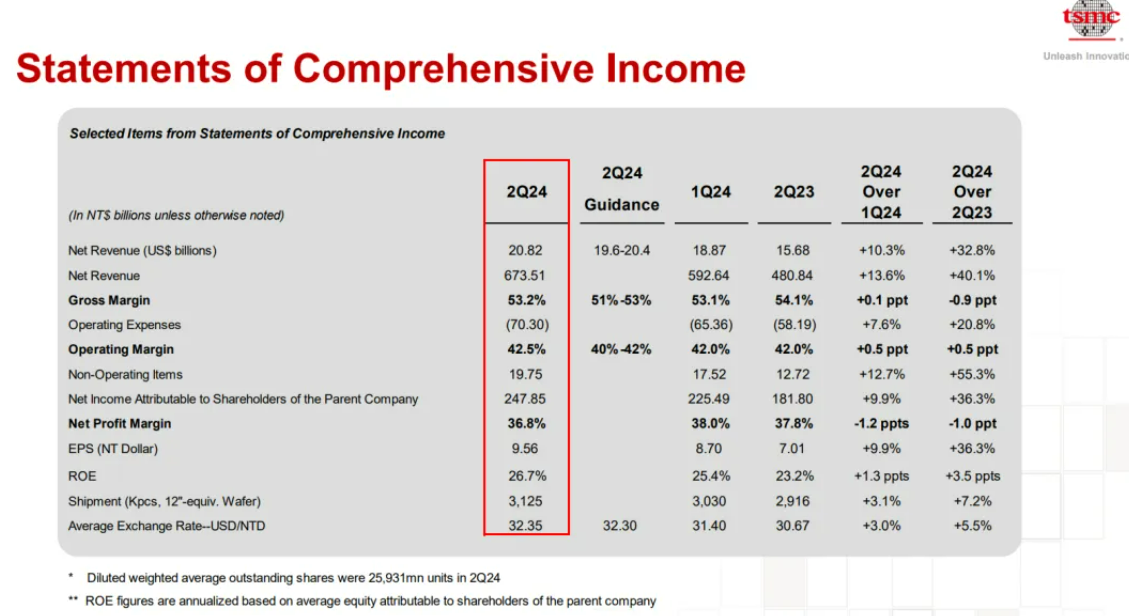

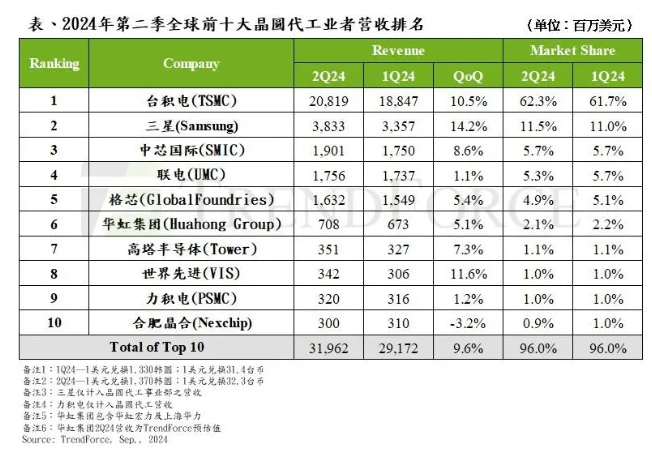

十大晶圆代工排名!

关键词:

行业新闻

晶圆抛光都有哪些方法?

关键词:

行业新闻

东芝12寸晶圆工厂竣工!

关键词:

行业新闻

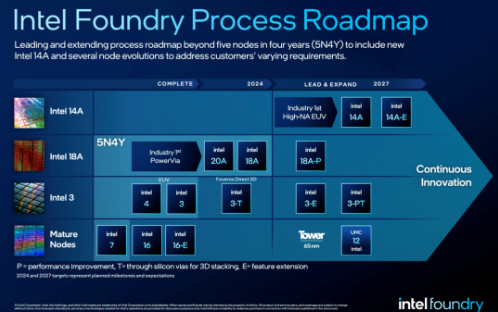

英特尔晶圆代工,更新路线图

关键词:

行业新闻

晶圆和芯片的关系是什么

关键词:

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| RB751G-40T2R | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| TPS63050YFFR | Texas Instruments | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor |

热门标签

ROHM

Aavid

Averlogic

开发板

SUSUMU

NXP

PCB

传感器

半导体

资讯排行榜

关于我们

AMEYA360公众号二维码

识别二维码,即可关注

AMEYA360商城(www.ameya360.com)上线于2011年,现有超过3500家优质供应商,收录600万种产品型号数据,100多万种元器件库存可供选购,产品覆盖MCU+存储器+电源芯 片+IGBT+MOS管+运放+射频蓝牙+传感器+电阻电容电感+连接器等多个领域,平台主营业务涵盖电子元器件现货销售、BOM配单及提供产品配套资料等,为广大客户提供一站式购销服务。